Streamline Migration, Fast Deployment and Cost Effective

KBEnetz stands apart from everyone

A Group of ASIC & AI Experts

Veteran RF/Analog/Mixed-Signal engineers integrating modern AI into silicon design.AI-Powered IC Design Engineering

Data-driven models and optimization that accelerate design cycles and improve PPA.

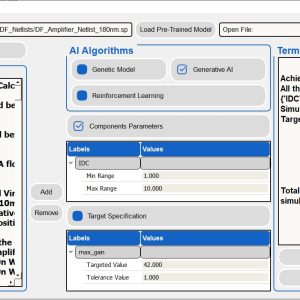

AICO AI Model Generator

- Explore AICO

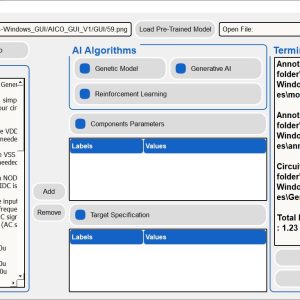

Create AI models of your schematic IPs directly from your design environment. - Model from Simulated & Measured Data

Train circuit models using both simulation (Cadence/Ngspice) and lab results. - Image → Netlist Conversion

Generate editable netlists from schematic images with AICO.

Circuit Modeling & Verificationr

AI-Driven Circuit Model Generation

Fast, accurate RF/Analog circuit models for system-level exploration.PVT Difference Analysis

AI maps measurement results to simulations for robust corner & variability insight.Mixed-Signal IC Verification

ML-assisted checks and model abstraction to speed up verification closure.

Flow Automation & Tooling

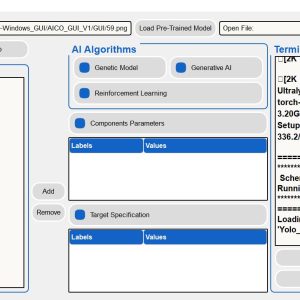

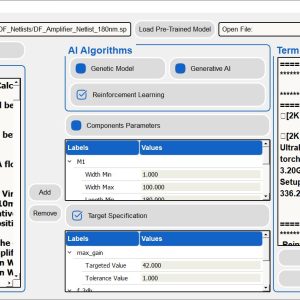

Cadence/Ngspice Integration

Use AICO within Cadence/Ngspice to extract datasets for RL/GenAI models.Python ↔ Cadence SKILL Bridge (Open-Source)

Automated testbench creation, sweeps, and data pipelines across tools.Custom AI in Your Flow

Plug GenAI & Reinforcement Learning into existing analog design workflows.

Design & Implementation Services

- Analog Schematics & Layout

End-to-end block design with AI-guided optimization for speed and power. - ASIC Design & Verification

Architecture definition, RTL/DFT, and verification with AI accelerators. - FPGA → ASIC Migration

Cost, speed, and power advantages via structured migration plans.

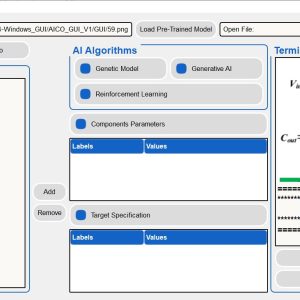

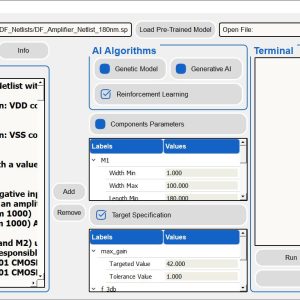

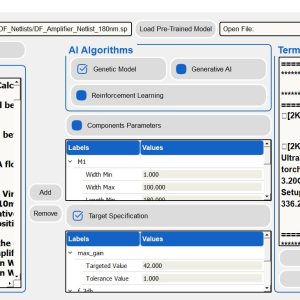

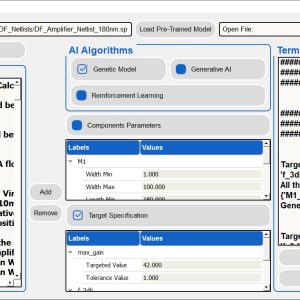

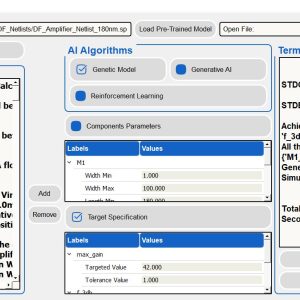

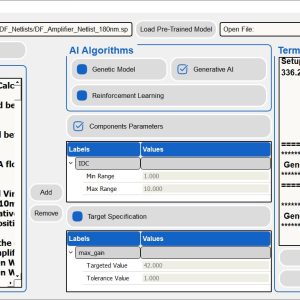

Algorithms We Use (Tailored per Project)

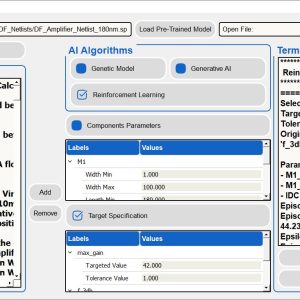

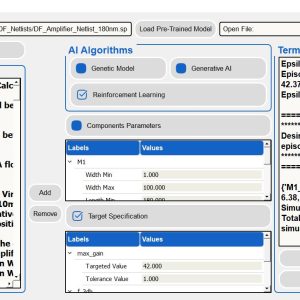

Reinforcement Learning (RL) — Closed-loop tuning & design space exploration.

Generative AI (GANs, Autoencoders) — Synthetic data & model generation.

Transformers — Advanced perception for EDA artifacts and documents.

YOLO / CV Stack — Schematic/wafer imagery parsing and QA.

Genetic Algorithms & SVM/Bayesian — Global optimization & robust classification.

Watch Our Algorithms in Action

How It Works (Process)

Ingest — Pull schematics/netlists & measurements from your tools and benches.

Generate — Build AI/ML circuit models (AICO) from simulated + measured data.

Validate — Cross-check against PVT corners, golden benches, and silicon.

Optimize — RL/Genetic methods tune design parameters for target specs.

Deploy — Drop-in models and automated benches back into your CAD flow.